# EGR 234 – Digital Logic Design Lab 5: Digital Logic Circuit Design Using the DE2 Board

Lab Report by: Christopher Parisi Lab Partner: No Partner October 8, 2010

## **Exercise**

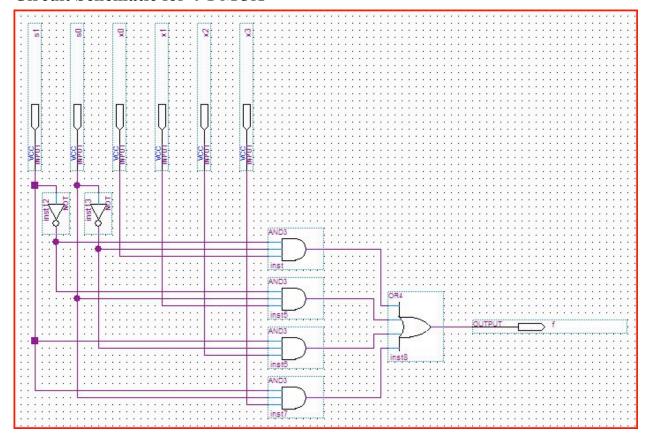

## **Circuit Schematic for 4-1 MUX**

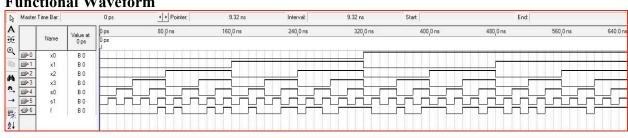

### **Functional Waveform**

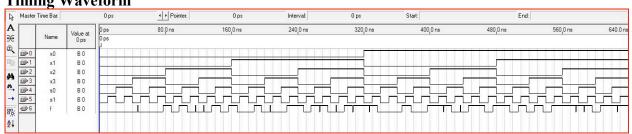

**Timing Waveform**

# **Truth Table**

| X0 | X1 | X2 | Х3 | S0 | <b>S</b> 1 | f |

|----|----|----|----|----|------------|---|

| 0  | 0  | 0  | 0  | 0  | 0          | 0 |

| 0  | 0  | 0  | 0  | 0  | 1          | 0 |

| 0  | 0  | 0  | 0  | 1  | 0          | 0 |

| 0  | 0  | 0  | 0  | 1  | 1          | 0 |

| 0  | 0  | 0  | 1  | 0  | 0          | 0 |

| 0  | 0  | 0  | 1  | 0  | 1          | 0 |

| 0  | 0  | 0  | 1  | 1  | 0          | 0 |

| 0  | 0  | 0  | 1  | 1  | 1          | 1 |

| 0  | 0  | 1  | 0  | 0  | 0          | 0 |

| 0  | 0  | 1  | 0  | 0  | 1          | 1 |

| 0  | 0  | 1  | 0  | 1  | 0          | 0 |

| 0  | 0  | 1  | 0  | 1  | 1          | 0 |

| 0  | 0  | 1  | 1  | 0  | 0          | 0 |

| 0  | 0  | 1  | 1  | 0  | 1          | 1 |

| 0  | 0  | 1  | 1  | 1  | 0          | 0 |

| 0  | 0  | 1  | 1  | 1  | 1          | 1 |

| 0  | 1  | 0  | 0  | 0  | 0          | 0 |

| 0  | 1  | 0  | 0  | 0  | 1          | 0 |

| 0  | 1  | 0  | 0  | 1  | 0          | 1 |

| 0  | 1  | 0  | 0  | 1  | 1          | 0 |

| 0  | 1  | 0  | 1  | 0  | 0          | 0 |

| 0  | 1  | 0  | 1  | 0  | 1          | 0 |

| 0  | 1  | 0  | 1  | 1  | 0          | 1 |

| 0  | 1  | 0  | 1  | 1  | 1          | 1 |

| 0  | 1  | 1  | 0  | 0  | 0          | 0 |

| 0  | 1  | 1  | 0  | 0  | 1          | 1 |

| 0  | 1  | 1  | 0  | 1  | 0          | 1 |

| 0  | 1  | 1  | 0  | 1  | 1          | 0 |

| 0  | 1  | 1  | 1  | 0  | 0          | 0 |

| 0  | 1  | 1  | 1  | 0  | 1          | 1 |

| 0  | 1  | 1  | 1  | 1  | 0          | 1 |

| 0  | 1  | 1  | 1  | 1  | 1          | 1 |

| 1  | 0  | 0  | 0  | 0  | 0          | 1 |

| 1  | 0  | 0  | 0  | 0  | 1          | 0 |

| 1  | 0  | 0  | 0  | 1  | 0          | 0 |

| 1  | 0  | 0  | 0  | 1  | 1          | 0 |

| 1  | 0  | 0  | 1  | 0  | 0          | 1 |

| 1  | 0  | 0  | 1  | 0  | 1          | 0 |

| 1  | 0  | 0  | 1  | 1  | 0          | 0 |

| 1  | 0  | 0  | 1  | 1  | 1          | 1 |

| 1  | 0  | 1  | 0  | 0  | 0          | 1 |

| 1  | 0  | 1  | 0  | 0  | 1          | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 |

The truth table shows the 64 different outputs of the 4-1 MUX. This truth table matches up to the results of the waveform. The results also match up to the DE2 Board LED's. This shows the Quartus II program is able to accurately represent a 4-1 MUX and upload the logical circuit to the Cyclone II chip.